## MATLAB<sup>®</sup> and Simulink<sup>®</sup> for Embedded System Design

Pieter J. Mosterman pieter.mosterman@mathworks.com

Senior Research Scientist The MathWorks, Inc.

# Introduction

- Increasing complexity of embedded systems

- Complexity

- Intricacy

- Size

- Raising the Level of Abstraction

- Compilers to handle the complexity because of size

## Agenda

- The System Design Challenge

- Software Design Flow

- Hardware Design Flow

- Summary

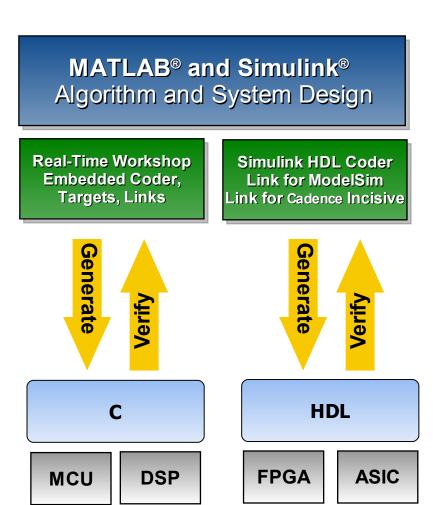

## The System Design Challenge

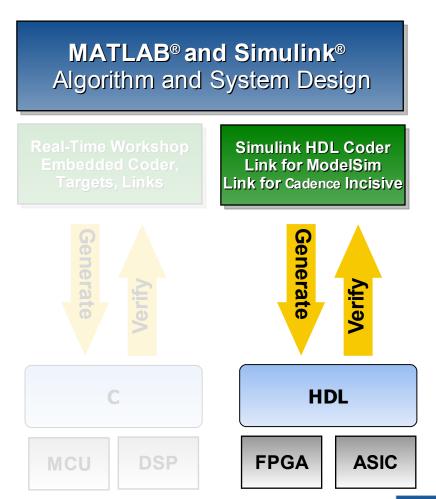

We design, simulate, and validate system models and algorithms in MATLAB<sup>®</sup> and/or Simulink<sup>®</sup>

he MathWorks

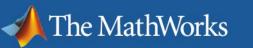

- How can we implement and verify designs on DSPs and GPPs?

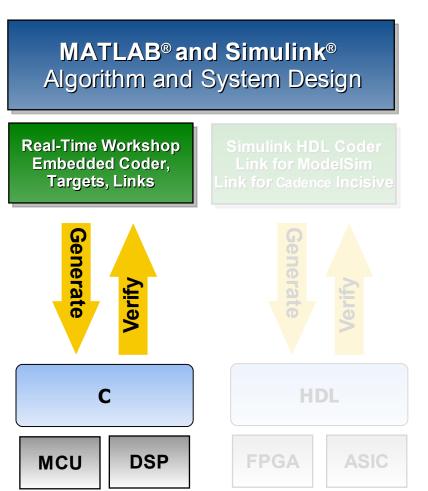

- How can we implement and verify designs on FPGAs and ASICs?

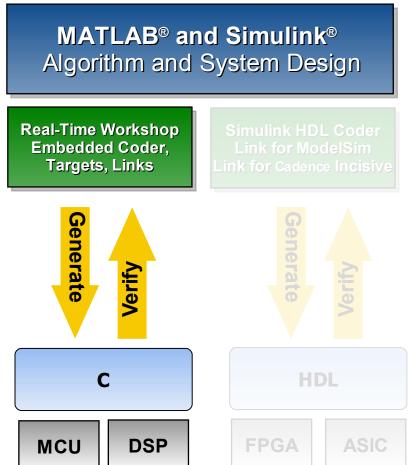

MATLAB<sup>®</sup> and Simulink<sup>®</sup> Algorithm and System Design

# Integrated Design Flow for Embedded Software and Hardware

- Design, simulate, and validate system models and algorithms in MATLAB and Simulink

- Automatically generate C and HDL

- Verify hardware and software implementations against the system and algorithm models

# Agenda

- The System Design Challenge

- Software Design Flow

- Hardware Design Flow

- Summary

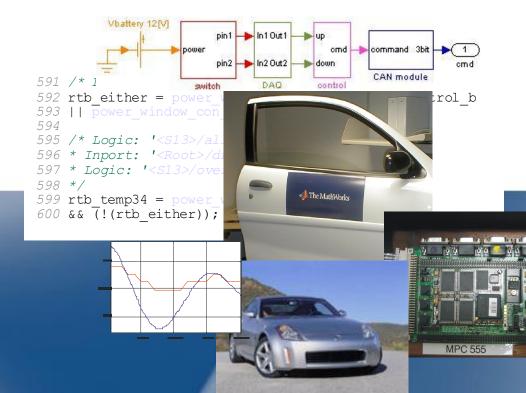

# Integrated Design Flow for Embedded Software

- Implementation with automatic C code generation

- Implementation

The MathWorks

- Floating- and fixed-point code

- Integration with downstream IDEs and tools

- Links to verification

- Device drivers

- Optimization options

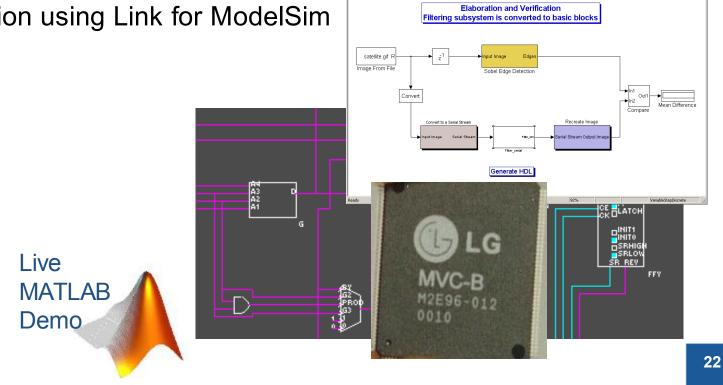

# Representative Application – Video

Live

MATI AB

Demo

- Video system design and implementation

- Encapsulates challenges: complexity, convergence, time-to-market

- Sophisticated algorithms

he MathWorks

- Floating- and fixed-point issues

- DSP or FPGA/ASIC implementations

- Design flows and steps shown directly applicable to other signal processing applications

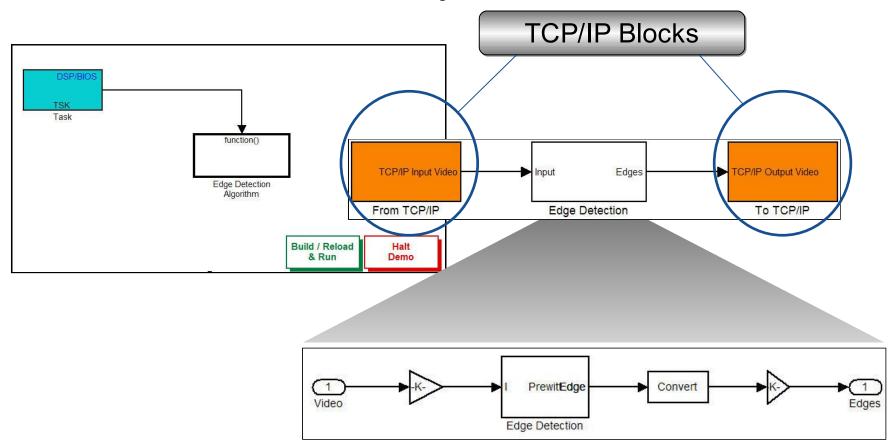

Embedded Software Case Study: Video Edge Detection on a DSP

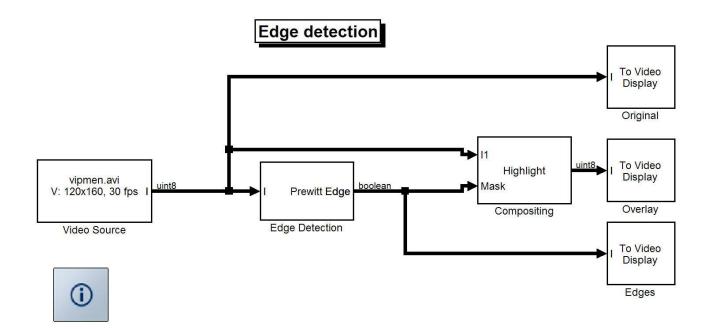

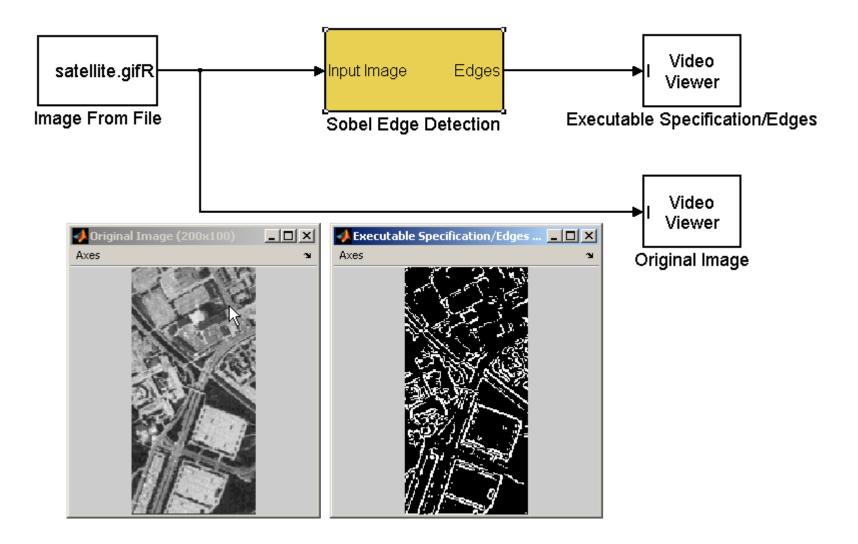

# Example: Video Edge Detection

- Floating point video edge detection system based on Prewitt algorithm

- Compositing original image with detected edges

- Utilizes blocks from Video and Image Processing Blockset

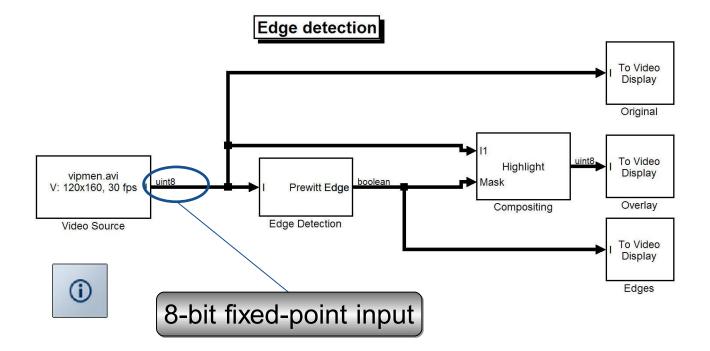

# **Converting to Fixed-Point**

The MathWorks

- Polymorphic blocks capable of floating- and fixed-point operation

- 8-bit input datatype blocks inherit fixed-point data

- Simulink Accelerator provides fast fixed-point simulation

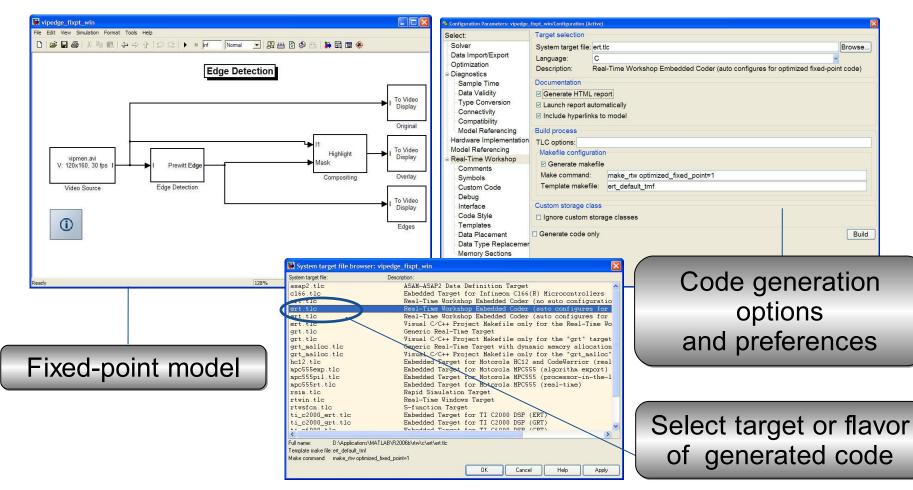

# Automatic Code Generation for Implementation on GPPs and DSPs

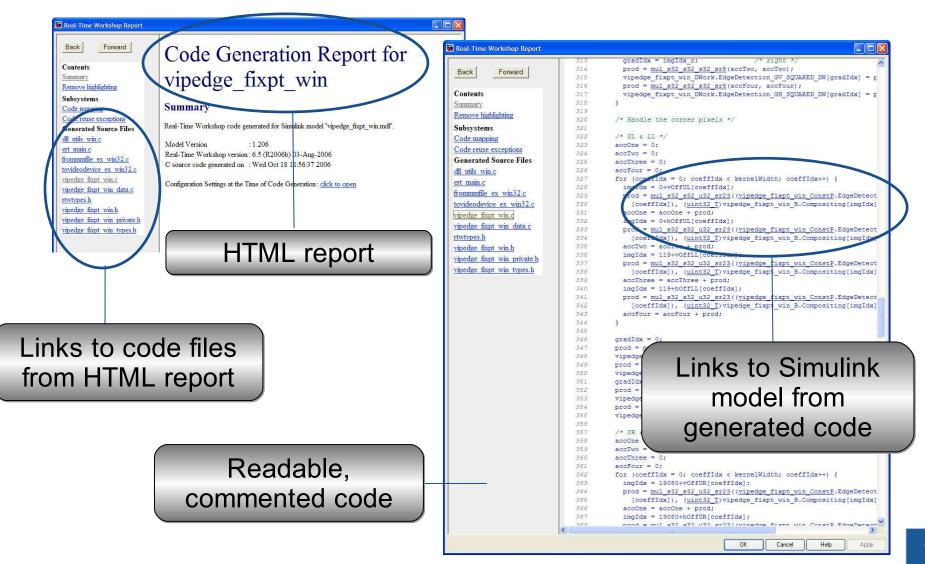

## **Code Generation Report**

#### Video Edge Detection Embedded Software System on TI 6000<sup>™</sup>

The MathWorks

# Code Execution on Target and Profiling

- Build and execute

- Auto-generate C and ASM

- Integrate RTOS and scheduler

- Create full CCS project

- Invoke compiler, linker, and download code

- Run on target

- Profile code performance

System profiling includes entire DSP application code

| ) | 16.03 ms |  |  |  |  |  |  |  |

|---|----------|--|--|--|--|--|--|--|

|   | 8.02%    |  |  |  |  |  |  |  |

|   | 118      |  |  |  |  |  |  |  |

| Ec | dit Vie                                                                           | 1          | 1212       | bug Des      | -            |                                                          |                                                     | 5 K |

|----|-----------------------------------------------------------------------------------|------------|------------|--------------|--------------|----------------------------------------------------------|-----------------------------------------------------|-----|

| mþ | 0                                                                                 | 8          | đ <b>i</b> |              |              |                                                          | nos/VIPBlks/EdgeOverlayFlow_on_DSP/targetModel2_c6C |     |

|    | Num                                                                               | ber of     | iter       | ations       | ounted       | ]1                                                       | 118                                                 |     |

|    |                                                                                   |            |            |              |              |                                                          |                                                     |     |

|    | System name                                                                       |            |            |              |              | targetModel3/Edge Detection Algorithm/Edge<br>Detection1 |                                                     |     |

|    | STS                                                                               | STS object |            |              |              |                                                          | sts <u>Svs</u> 0_OutputUpdate                       |     |

|    | Max time spent in this subsystem<br>per interrupt<br>Max percent of base interval |            |            | subsyste     |              | 16.03 ms                                                 |                                                     |     |

|    |                                                                                   |            |            | nterval      | 1            | 3.02%                                                    |                                                     |     |

|    | Num                                                                               | ber of     | iter       | ations       | ounted       | $\boldsymbol{\lambda}$                                   | 118                                                 |     |

|    |                                                                                   |            |            |              | /            |                                                          |                                                     |     |

|    | System name                                                                       |            | t          | targetModel3 |              |                                                          |                                                     |     |

|    | STS object                                                                        |            |            |              | 5            | stsSys2_OutputUpdate                                     |                                                     |     |

|    | Max time spent in this subsystem per interrupt                                    |            | m /2       | 244.4 ns     |              |                                                          |                                                     |     |

|    | Max percent of base interval<br>Nuprber of iterations counted                     |            |            | nterval      |              | 0.000122%                                                |                                                     |     |

|    |                                                                                   |            |            | counted      | N            | 102                                                      |                                                     |     |

|    |                                                                                   |            | 1          |              |              |                                                          | 1                                                   |     |

|    |                                                                                   |            |            | nier<br>Mier | 4 ns<br>0122 | 2.<br>7755                                               | Subsystem profi                                     | lir |

|    |                                                                                   |            |            |              |              | 225                                                      |                                                     |     |

|    |                                                                                   |            | 11.2       | 02           |              |                                                          |                                                     |     |

he MathWorks

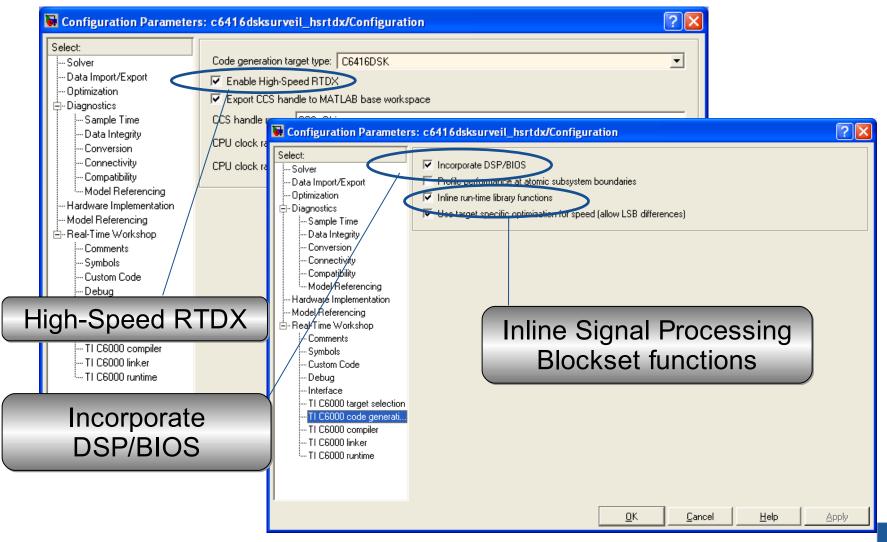

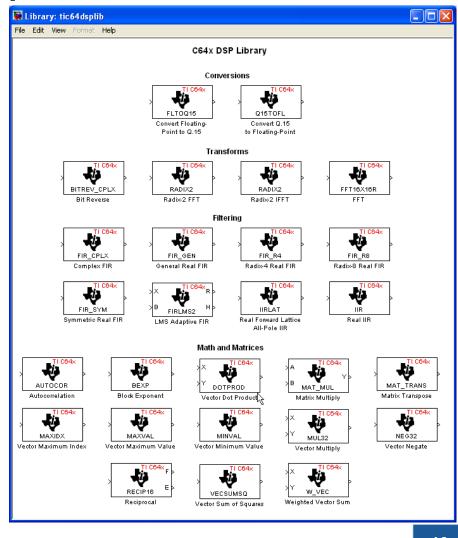

# **Code Optimization Options**

- Utilize target-specific blocks

- C-callable assembler libraries

- Simulate bit-true in Simulink

- Generate calls to hand-optimized assembler libraries

- Highly optimized implementation of core functionality

- C62x and C64x fixed-point DSPs

- Manual optimization by user

The MathWorks

```

40

Visualize and debug embedded

41

% Initialize motion threshold

42 - global newThresh

software with MATLAB

43 - lastThresh = 0;

44 - newThresh = 1.5e5;

45

46

% Connect to CCS

47 - CCS Obj = connectToCCS(modelName);

48 - saved visibility = CCS_Obj.isvisible;

49 - CCS Obj.visible(1);

50

51 % Load application

52 - loadApp(modelName, CCS Obj);

53

54 % Run application

55 - fprintf('Running application: %s\n', modelName);

56 -

CCS Obj.run;

57

58 - pause(3);

59

60 % Connect to the target

Original

Edge

61 - userPrompt = sprintf('Please enter the IP address or the host pame of the %s board: '

62 - hostName = input(userPrompt, 's');

63 - port = 49000;

64 - fprintf('Connecting to TCP/IP server at: "%s:%d"\n', hostName, port)

Captured

65 - connfd = tcpip(hostName, port);

Input video

66 - set(connfd, 'OutputBufferSize', 64000);

video

67 - set(connfd, 'InputBufferSize', 64000);

68 - try

69 -

fopen(connfd);

70 - catch

71 -

fprintf('Cannot established TCP/IP connection to "%s:%d".\n', hostName, port);

72 -

fprintf('Terminating demo.\n');

73 -

return;

74 - end

75 - set(connfd, 'ByteOrder', 'littleEndian');

MATLAB script

fprintf('Established TCP/IP connection to "%s:%d"\n', hostName, port);

76 -

(test bench)

```

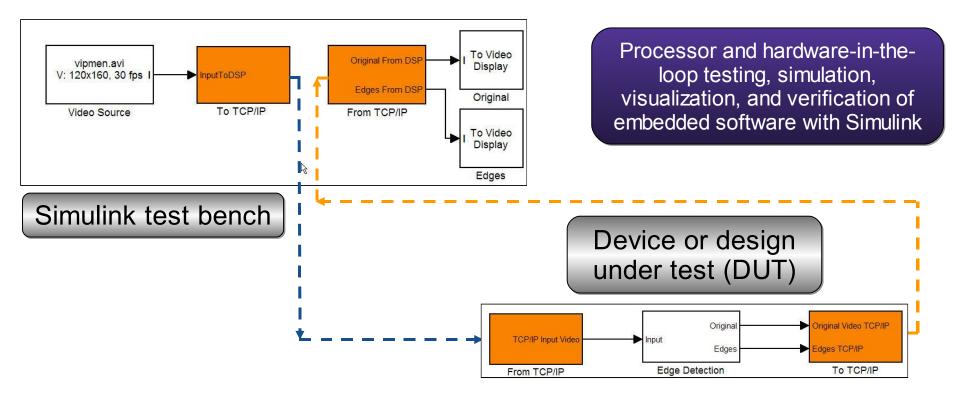

#### Design Verification and Visualization: Simulink as software test bench

The MathWorks

Simulink system design embedded on DSP

# Review: Integrated Design Flow for Embedded Software

- Drive system development with an executable specification

- Quickly create complete working code base

- Use code profiles to identify and optimize bottlenecks

- Verify code with Links to IDEs and processors

# Agenda

- The System Design Challenge

- Software Design Flow

- Hardware Design Flow

- Summary

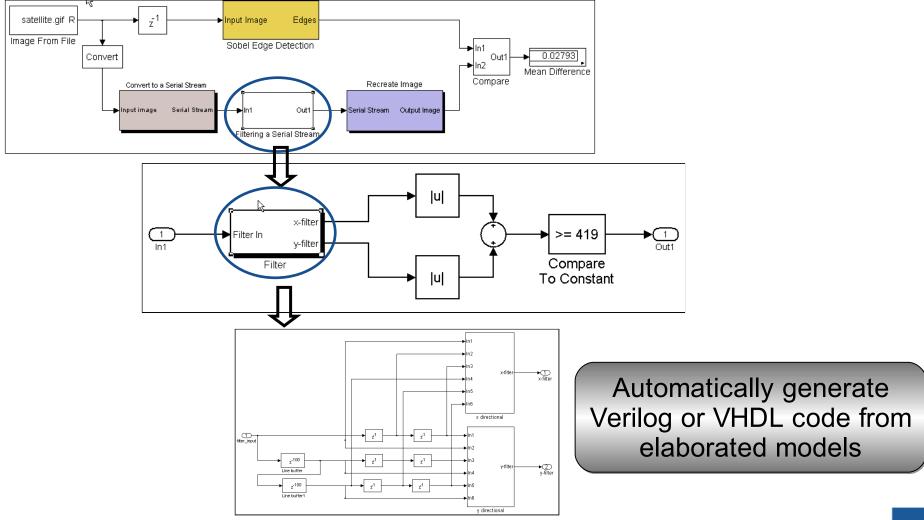

# Integrated Design Flow for Hardware (FPGA and ASIC)

- Design elaboration

- Implementation

- HDL code generation (VHDL and Verilog)

- test bench generation

- Links to verification

- Integration with synthesis tools

# What We Will Show In This Case Study

- Behavioral modeling and simulation

- Fixed-point modeling and simulation

- **Design elaboration**

- HDL generation

he MathWorks

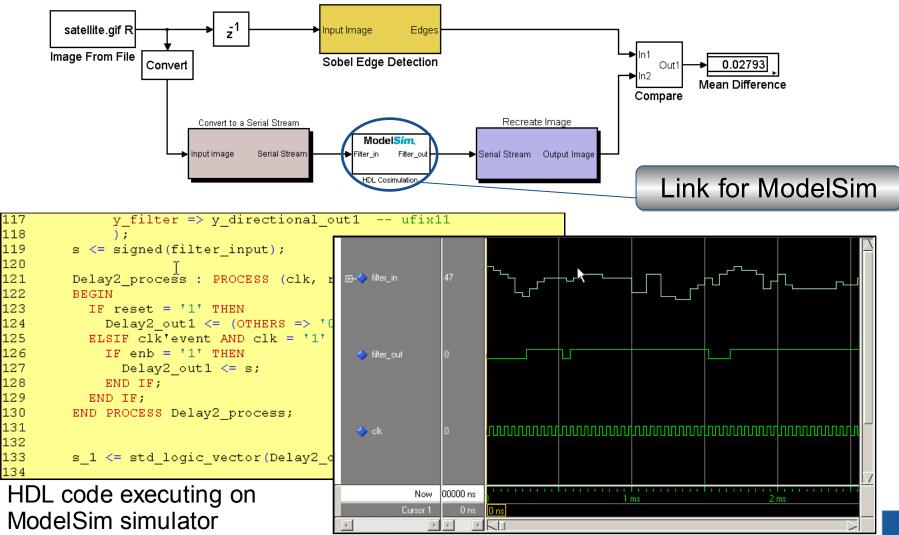

Co-simulation using Link for ModelSim

Hardware Case Study: Video Edge Detection on an FPGA

- 🗆 ×

#### **Executable Specification**

# **Design Elaboration**

# HDL Code Generation Using GUI

| 🍓 Configuration Paramete                                                                                       | ers: edge_detection_ready_to_use_SHC/Configuration (Ac                                                       | tive)                                        |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Select:                                                                                                        | Code generation control file                                                                                 |                                              |

| Solver<br>Data Import/Export<br>Optimization<br>Diagnostics                                                    | File name:                                                                                                   | Load<br>Save                                 |

| Sample Time<br>Data Validity<br>Type Conversion<br>Connectivity<br>Compatibility                               | Target<br>Generate HDL for: edge_detection_ready_to_use_SHS/Filter_st<br>Language: vhdl<br>Directory: hdlsrc | Select subsystem, target language, directory |

| Model Referencing<br>Hardware Implementation<br>Model Referencing<br>Real-Time Workshop<br>Comments<br>Symbols | Code generation output<br>© Generate HDL code<br>© Display generated model only                              | Select output options                        |

| ← Custom Code<br>← Debug<br>← Interface<br>← HDL Coder<br>← Global Settings<br>← Test Bench                    | C Generate HDL and display generated model Restore Factory Defaults                                          | Run Compatibility Checker<br>Generate        |

| Check mo                                                                                                       | odel for errors                                                                                              | Generate HDL Code                            |

| ,                                                                                                              | ОК                                                                                                           | Cancel Help Apply                            |

# More Code Generation Options

| 🍓 Configuration Parameter                                                                                                                                       | rs: edge_detection_ready_to_use_SHC/Configuration (Active)                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select:                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                 |

| Solver<br>Data Import/Export<br>Optimization<br>Diagnostics                                                                                                     | Reset type:       Asynchronous       Reset asserted level:       Active-high         Clock input port:       clk       Clock enable port:       clk_enable         Reset input port:       reset       clock enable       clock enable                                                                                                                          |

| Sample Time<br>Data Validity<br>Type Conversion<br>Connectivity                                                                                                 | Additional settings<br>General Ports Advanced Select reset and clock options                                                                                                                                                                                                                                                                                    |

| Compatibility     Model Referencing     Hardware Implementation     Model Referencing     Real-Time Workshop     Comments     Symbols     Custom Code     Debug | General         Comment in header:         Verilog file extension:         .v         VHDL file extension:         .vhd         Entry conflict postfix:         _entity         Package postfix:         _pkg         Reserved word postfix:         _rsvd         Clocked process postfix:         _process         Split entity file postfix:         _entity |

| ⊡nterface<br>⊡-HDL Coder<br>⊡-Global Settings<br>Test Bench                                                                                                     | Split arch file postfix: arch<br>Set language-specific<br>options: input/output<br>datatypes, timescale<br>directives,                                                                                                                                                                                                                                          |

| ,                                                                                                                                                               | OK Cancel Help Apply                                                                                                                                                                                                                                                                                                                                            |

# Automatically Generate Test Bench

| 🍇 Configuration Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rs: hdlcoderlms/Configuration (Active)                                                                                                                                                   | x                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Select:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Test bench                                                                                                                                                                               |                                 |

| Solver     Data Import/Export     Optimization     O | Test bench name postfix:       _tb         ✓ Force clock       Clock high time (ns):         ✓ Force clock enable       5         ✓ Force reset       Hold time (ns):         12       2 | -                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>D</u> K <u>C</u> ar                                                                                                                                                                   | icel <u>H</u> elp <u>A</u> pply |

## **Co-simulate Generated HDL**

# Review: Integrated Design Flow for Hardware

- Drive system development with an executable specification

- Quickly create complete working HDL code base and test benches

- Verify code with Links to RTL simulators and synthesis tools

# Agenda

- The System Design Challenge

- Software Design Flow

- Hardware Design Flow

- Summary

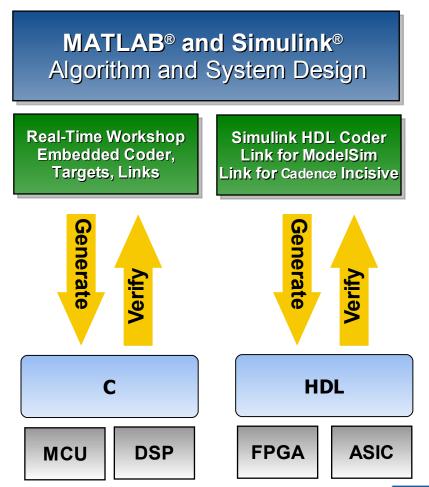

# Summary

- Accelerate development using Model-Based Design

- Generate

- Real-Time Workshop

- Simulink HDL Coder

- Verify

- Link for Cadence Incisive

- Design and verify software and hardware from MATLAB and Simulink