## ECE 477 LAB 7

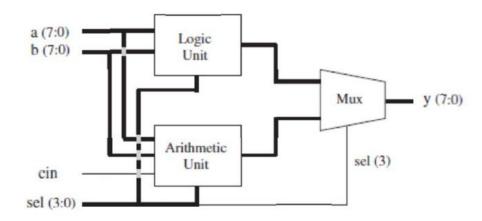

1) In the below figure a sample Arithmetic Logic Unit (ALU) and its truth table are presented. Write down the VHDL code of this ALU and do related simulations.

| sel  | Operation       | Function               | Unit       |

|------|-----------------|------------------------|------------|

| 0000 | y <= a          | Transfer a             |            |

| 0001 | y <= a+1        | Increment a            |            |

| 0010 | y <= a-1        | Decrement a            |            |

| 0011 | y <= b          | Transfer b             | Arithmetic |

| 0100 | $y \le b+1$     | Increment b            |            |

| 0101 | y <= b-1        | Decrement b            |            |

| 0110 | $y \le a+b$     | Add a and b            |            |

| 0111 | y <= a+b+cin    | Add a and b with carry |            |

| 1000 | y <= NOT a      | Complement a           |            |

| 1001 | y <= NOT b      | Complement b           |            |

| 1010 | $y \le a AND b$ | AND                    |            |

| 1011 | y <= a OR b     | OR                     | Logic      |

| 1100 | y <= a NAND b   | NAND                   |            |

| 1101 | y <= a NOR b    | NOR                    |            |

| 1110 | y <= a XOR b    | XOR                    |            |

| 1111 | y <= a XNOR b   | XNOR                   |            |

Figure-1 : An ALU design

## <u>Homework</u>

No homework.